目前,虽然已经有了一些针对FPGA开发的开源程序,例如Symbiflow、Yosys。但FPGA供应商通常只为想要在其芯片上工作的开发人员提供“闭源程序”,所以,这还是有一定程度的局限性的。

不过,赛灵思最近采取的行动却突破了这一局限。他们通过发布Vitis HLS前端的源代码来履行其“支持开发人员和研究人员开源计划的承诺”。

Vitis HLS究竟是什么?

在我们查看源代码发布之前,我们可能想知道Vitis HLS究竟做了什么。该公司将Vitis HLS描述为一种高级综合(HLS)工具,其允许 C、C++ 和OpenCL函数硬连线到设备逻辑结构和RAM/DSP块上。Vitis HLS在Vitis应用加速开发流程中实现硬件内核,并在公司的Vivado Design Suite中使用C/C++代码为FPGA设计开发RTL IP 。

Vitis HLS设计流程如下:

- 编译、模拟和调试C/C++算法。

- 查看报告以分析和优化设计。

- 将C算法综合到 RTL 设计中。

- 使用RTL协同仿真来验证RTL的实现。

- 将RTL实现打包到编译后的目标文件( .xo )扩展名中,或导出到RTL IP。

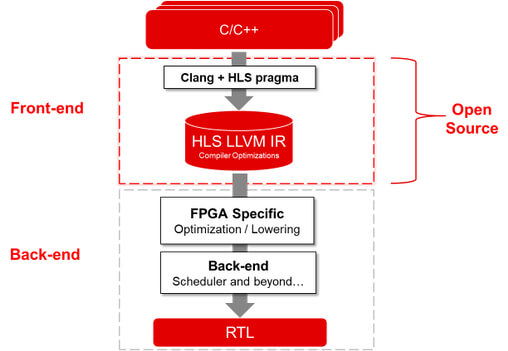

部分开源版本

该版本中的一个关键词是“前端”,因为 Vitis HLS 后端在RTL代码生成之前处理FPGA的特定优化和调度仍然是闭源的。

尽管如此,前端源代码将允许软件和硬件开发人员使用标准的Clang/LLVM基础设施,同时自定义设计流程以添加对新高级语言、新的特定领域优化编译指示或编译器指令的支持,并自定义对LLVM IR(中间表示)的转换。Vitis HLS前端的源代码可以在Github上找到。

Vitis HLS前端的开源版本已经被提前收到代码的公司和大学使用。Silexica的 SLX插件扩展了Vitis HLS 2020.2代码转换,以改善Vitis HLS带来的延迟和吞吐量结果,而伊利诺伊大学厄巴纳香槟分校集成了新的Clang pragma和LLVM以进行评估。伦敦帝国理工学院的一名博士生利用该代码将其动态和静态调度 (DASS) 集成到HLS流程中。香港科技大学(HKUST)开发了两个项目,即“高效自动优化通过阶段排序”和“Multi-FPGA HLS”,分别使用机器学习和启发式算法来提高性能和资源消耗,以及与网络或DDR存储器互连的多个FPGA。

更多信息可在他们的公告中获得。

本文信息来源于EETimes。

文章翻译者:Jacob,嵌入式系统测试工程师、RAK高级工程师,物联网行业多年工作经验,熟悉嵌入式开发、测试各个环节,对不同产品有自己专业的分析与评估。