备注1:AI 即Artificial Intelligence人工智能,本文均称为AI。它是研究、开发用于模拟、延伸和扩展人的智能的理论、方法、技术及应用系统的一门新的技术科学。

备注2:ML 即Machine Learning机器学习,本文均称为ML。它是研究计算机怎样模拟或实现人类的学习行为,以获取新的知识或技能,重新组织已有的知识结构使之不断改善自身的性能。常见的机器学习任务有:分类、输入缺失分类、回归、转录、机器翻译、结构化输出、异常检测、合成和采样、缺失值填补、去噪、密度估计等等。

处理器设计自动化领域的领导者Codasip公司,最近宣布推出了 L31 和 L11 低功耗嵌入式 RISC-V 处理器内核。该处理器内核可以为具有功耗和尺寸限制的定制化人工智能/机器学习(AI/ML)等物联网边缘应用程序进行优化。

该公司还解释说,新的 L31和L11 RISC-V 内核可以运行 Google 的TensorFlow Lite for Microcontrollers (简称 TFLite-Micro),而且可以通过 Codasip Studio RISC-V 设计工具针对特定的应用进行优化。据我了解,这个优化过程是可以由客户自己完成的。当然,这要归功于 Codasip 首席技术官 Zdeněk Přikryl 介绍的完整架构许可证。Zdeněk Přikryl 介绍的内容如下所示:

通过购买RISC-V处理器高级描述语言CodAL的授权,让Codasip的客户可以获得一套完整的架构许可,从而可去实现ISA和微体系架构的定制。随着新L11/31内核的问世,我们可以更方便地在尺寸最小和功率最低的嵌入式处理器设计中加入客户所需要的功能,比如边缘人工智能等。

定制化内核的功能对于 AI 和 ML 的应用很重要,因为数据类型、量化模型和性能要求因应用的不同也会有很大差异,而且现成的处理器可能无法针对特定任务进行优化。

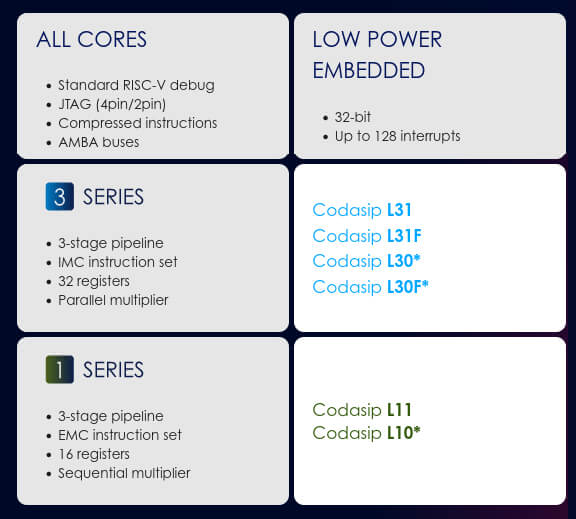

目前,我没有获得太多关于新内核的细节,暂时只知道它们都带有3-stage pipeline(管道计算模式)。Codasip L31/L31F(带 FPU)使用的是 RV32IMC指令集,可以提供 32 个寄存器和一个并行乘法器。而Codasip L11 依赖的是 RV32EMC 指令集,带有 16 个寄存器和一个顺序乘法器。另外,它们也取代了不再被推荐的早期 Codasip L30(F) 和 L10 内核。

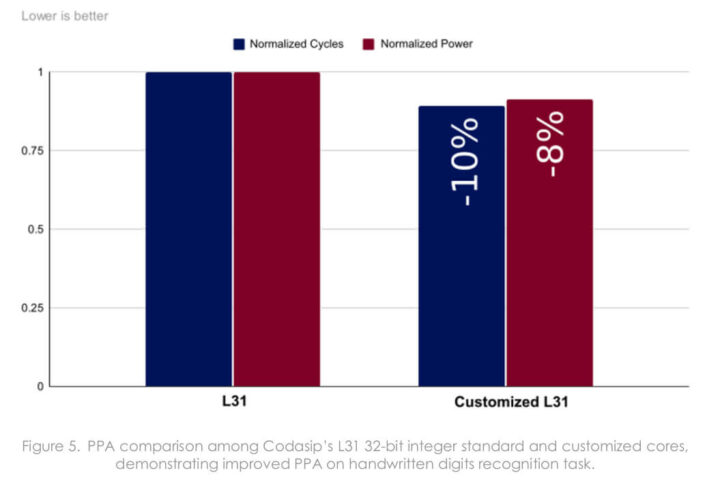

Codadip在题为“L系列内核上的嵌入式人工智能—由定制化指令授权的神经网络”白皮书中也展示了使用TFLite-Micro和定制的好处,不过需要注册获取,但其实你可以使用假的电子邮件。他们也以“MNIST 手写数字分类”为例,在周期、功率和面积等方面比较各种实现。

上图中,中间显示的是带有FPU (31F) L31芯片时的测试结果,可以看到其速度更快、功耗更少,但面积也会较大。对于这样的结果,可以有一个解决方案即:使用 L31 量化神经网络参数,输入数据并由TFLite-Micro 支持。这个解决方案性能与硬件 FPU 方案几乎是相同的,功耗甚至还要更低一些,但它还是没有改变内核,所以芯片面积也还是相同的。用整数代替浮点对精度的影响可以忽略不计:在一组有10,000张图片的组合中,它的准确率是98.91% (fp32)和98.89% (int8)。

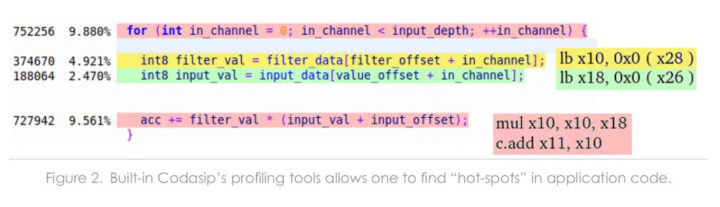

因此,最好的折中方案应该是将 L31 与 TFLite-Micro 结合使用,但为了进一步优化设计,该公司使用了 Codasip Studio 对程序进行了分析,从而来定位消耗最多周期的(C)代码和相关指令。

为了优化向量内存负载以及卷积乘法和累加的序列,他们添加了两条自定义指令:

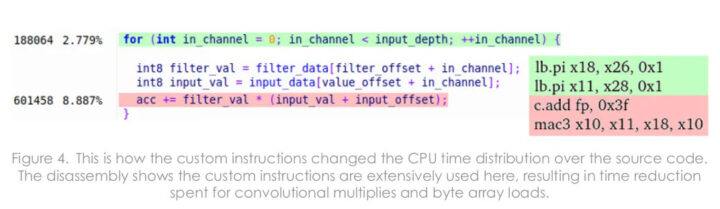

- mac3将乘法和加法加入单个时钟周期(加速上面的第四行)

- pi在加载指令之后立即增加地址(加入第 2 行和第 3 行)

新指令显示在配置文件中时,整个循环的运行周期少了很多。更具体地说,这导致循环次数减少了 10%、功耗降低了 8%。新的自定义指令尽管确实增加了面积,但也仅仅增加了0.8%。

Codasip RISC-V 微控制器对TFLite-Micro的支持真的算得上是一次成功的全新尝试,它现在也已经被添加到所有内核中了。

对于内核的评估用户则可以在运行裸机代码或 RTOS(如 FreeRTOS)的 Digilent Nexys A7 FPGA 板上完成。有关 L31 和 L11 RISC-V 内核的更多详细信息,你们可以在Codasip的网站和新闻稿中详细了解。

文章翻译者:Jacob,嵌入式系统测试工程师、RAK高级工程师,物联网行业多年工作经验,熟悉嵌入式开发、测试各个环节,对不同产品有自己专业的分析与评估。