备注:MIPS是一种采取精简指令集(RISC)的处理器架构,1981年出现,由MIPS科技公司开发并授权,广泛被使用在许多电子产品、网络设备、个人娱乐装置与商业装置上。最早的MIPS架构是32位,最新的版本已经变成64位。它的基本特点是:包含大量的寄存器、指令数和字符、可视的管道延时时隙,这些特性使MIPS架构能够提供最高的每平方毫米性能和当今SoC设计中最低的能耗。

曾经是全球三大芯片架构之一的MIPS现在似乎已经倒下了!没错,现在MIPS架构本身几乎不做任何事情了,而该公司也已经决定改用RISC-V架构,并发布了由eVocore P8700和I8500多处理器IP内核组成的eVocore产品阵容。

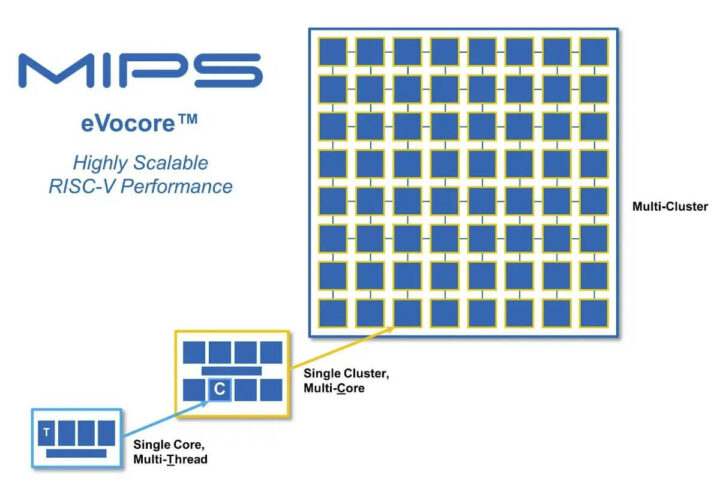

该64位内核可以从单核多线程扩展到具有多核的单集群、并扩展到多集群,目标是网络、数据中心和汽车等高性能、实时计算的应用场景。

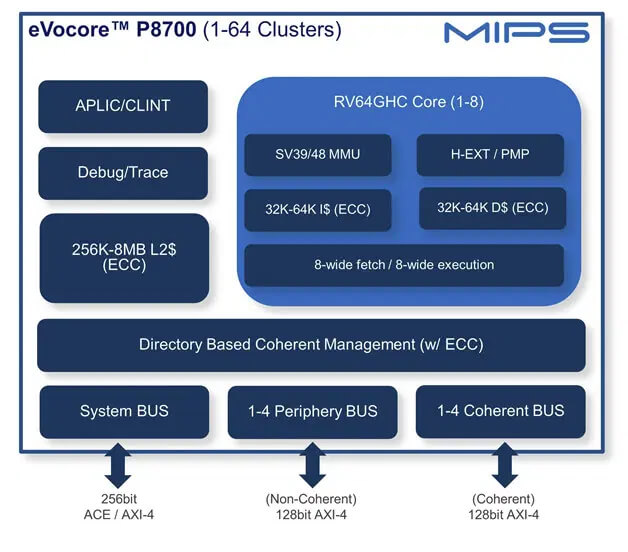

eVocore P8700将16级深度流水线(pipeline)与多问题无序(OOO)执行和多线程相结合。MIPS声称它的单线程性能比目前的其他RISC-V CPU IP产品中的性能要更高,不过他们没有没有提供任何数据证实这一点。我想它可能会用于云和高端服务器,因为它可以扩展到64个集群、512个内核和1,024个harts/threads。

P8700的亮点:

- 多线程的多问题超标量乱序(OOO)

- 用于更高时钟频率的16级深度流水线

- 8宽指令获取

- 8个执行管道:2xALU、MDU、2xFPU、2xMemory

- 具有L2缓存的增强型Coherence Manager

- 硬件预取、加宽总线、减少延迟

- 48位物理寻址

- 256中断支持,APLIC/CLINT

- 系统界面

- ACE或AXI:256位系统总线

- 可选:相干总线(最多8个端口)

- 可选:非相干外围总线(最多4个端口)

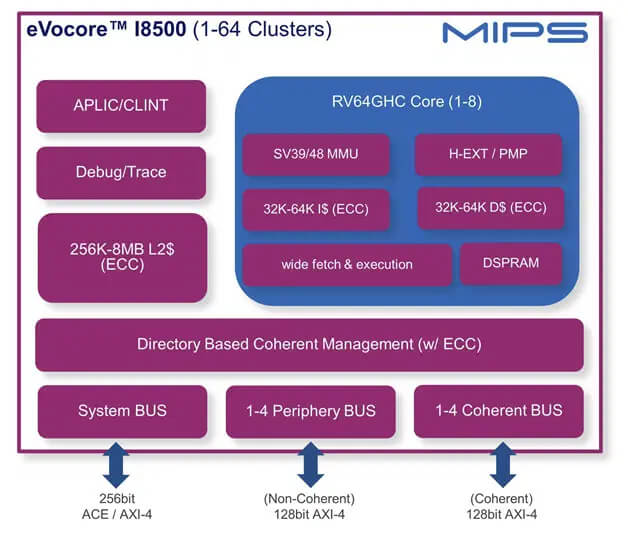

MIPS eVocore I8500 RISC-V内核主要通过用于SoC应用的有序多处理系统实现来“一流的性能效率”。每个I8500内核都结合了多线程和高效的三重问题流水线。

I8500的亮点:

- 同步多线程(SMT)有序

- 高效执行的9级流水线

- 宽指令获取

- 7个执行管道:ALU、MDU、2xFPU、2xMemory

- 具有L2缓存的增强型Coherence Manager

- 硬件预取、加宽总线、减少延迟

- 48位物理寻址

- 256中断支持,APLIC/CLINT

- 系统界面

- ACE或AXI:256位系统总线

- 可选:相干总线(最多8个端口)

- 可选:非相干外围总线(最多4个端口)

MIPS显然计划使用RISC-V用户定义指令(UDI)来添加额外的功能和加速器,同时与现成的RISC-V开发工具和软件库完全兼容。eVocore IP内核的其他特性包括特权硬件虚拟化、多线程、混合调试和功能安全。据我了解,该公司的这些产品预计将会用在汽车(ADAS、AV、IVI)、5G和无线网络、数据中心和存储,以及高性能的嵌入式应用。

eVocore P8700应该会在2022年第四季度上市,但他们目前没有提供eVocore I8500 IP预计上市的时间。如果你们感兴趣,在其产品页面上可以找到更多的详细信息。

本文消息来源于RISC-V博客。

文章翻译者:Jacob,嵌入式系统测试工程师、RAK高级工程师,物联网行业多年工作经验,熟悉嵌入式开发、测试各个环节,对不同产品有自己专业的分析与评估。