一直以来,开源 SoC 的设计都是可以在 FPGA 硬件上运行的,但由于成本太高,很少有人能把设计制作成实际使用的电路板。这就是为什么2020年Google SkyWater PDK(流程设计套件)与 efabless(集成电路设计、开发和商业化的创客社区平台)合作,并免费提供了多达100件的选定设计。

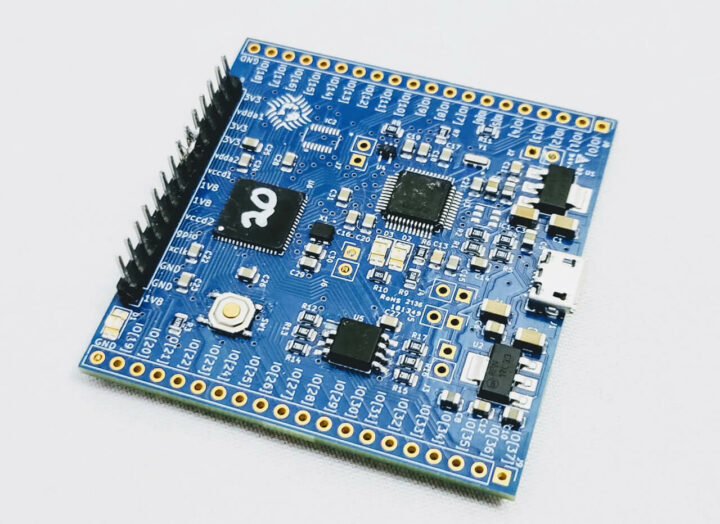

而efabless公司的chipIgnite计划就是由这一合作方案演变而来的。该方案提供了多种制造方案,比如:可以利用 9,750 美元制造出 100 个 QFN(方形扁平无引脚封装)或 300 个 WCSP(晶圆级芯片封装方式)零件;又或者以20,000 美元的价格制造出 1,000 个零件。efabless 公司的开源FPGA ASIC设计CLEAR就是基于该公司的Caravel模板SoC和openFPGA生成器框架制作的,其主要目的就是为了推广和展示chipIgnite“付费IC创作”解决方案。如果你们有需要,可以参加 GroupGets 上的团购活动去购买CLEAR开发板,现在的团购价是 74.99 美元,运费需要另外付。

开源FPGA ASIC—CLEAR的特性:

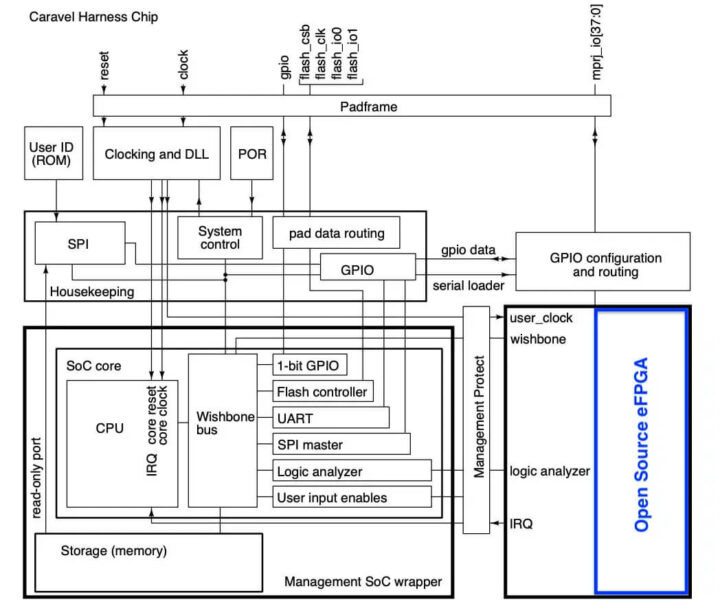

- FPGA – 小型 8×8 (64) CLB eFPGA

- CPU – 基于 VexRISCV 的 CPU

- 内存 – 3 KB 片上 RAM(2 kB OpenRAM 和 1 kB DFFRAM)

- 存储 – 外部 QSPI 闪存

- 外设 – SPI 主机、UART、39x 软件可配置 GPIO、计数器/定时器、逻辑分析仪

- 其他——可编程内部时钟频率

efabless 公司将重现所有开发步骤的工作流程信息:

- 基于 OpenFPGA 生成器框架生成嵌入式 FPGA 宏

- 将 eFPGA 宏集成到 Caravel 中,使其成为 FPGA ASIC – Clear

- SkyWater 代工厂通过chipIgnite程序制造ASIC

- 将 ASIC 封装并安装在其开发板上

- 使用开源 FPGA 编程软件测试开发板

我在这里展示流程信息,主要是为了向大家展示是如何做到这一点,从而帮助人们无需花费大量资金进行设计和制造,就能使用自己的定制 ASIC。第一个原型目前已经可以正常工作,如下面的视频所示。

相关视频链接,点击此处可查看。

据我了解,他们的团购活动会持续至 2022 年的 4 月 29 日,其销售目标是售出至少 200 个开发板。而他们的交付计划则定于9月,但具体的时间主要还是取决于4月的chipIgnite shuttle(2204C)计划,该计划需要达到最少的项目数量(最少项目数量是40个)才能继续往下进行。

文章翻译者:Jacob,嵌入式系统测试工程师、RAK高级工程师,物联网行业多年工作经验,熟悉嵌入式开发、测试各个环节,对不同产品有自己专业的分析与评估。