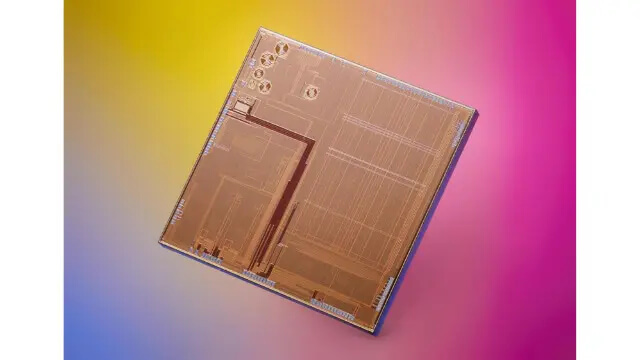

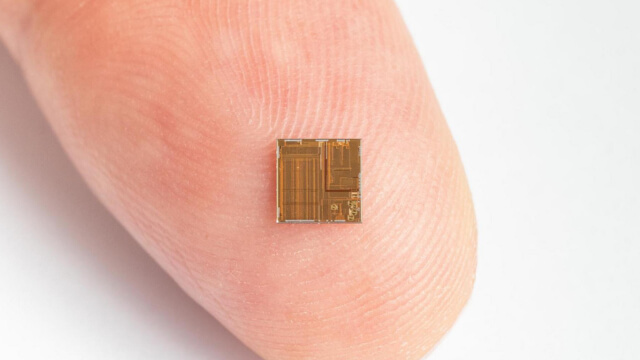

来自瑞士的CSEM 和来自日本的USJC 两家半导体公司之前共同开发过一款用于可穿戴电子产品的超低功耗 RISC-V 芯片。其实,这两家半导体公司做这类产品已经有一段时间了,它们都专注于低功耗芯片的技术开发。最近,他们一起合作的项目就使用了自适应体偏置 (ABB) 和深度耗尽通道 (DDC) 来构建了一款具有全部必需组件的超低功耗RISC-V 芯片。

自适应体偏置(Adaptive Body Biasing)其实源于 CSEM 实验室,它影响芯片所有在 ON、Standby 和 OFF 模式的运行效率。一般情况下,SoC在待机和关闭操作模式下会存在漏电问题,而自适应主体偏置技术则有助于在OFF模式下最大限度地减少漏电,同时在ON模式下保持最佳性能。

对于大多数芯片而言,处理器在等待数据传入或提供下一个事件期间会处于待机模式。在这种情况下,就会出现大量功率泄漏并可能会降低芯片的性能。而超低功耗芯片的自适应体偏置设计则可以减少这期间的功率泄漏量。由于当前的消息还比较有限,目前我只能根据EENews Europe的报道了解。据我所知,该芯片在慢速模式(见下文)下功耗可低至 10μA,在待机模式下,功耗约为1pW/bit。

该款芯片在 0.6V 的阈值电压下运行,并采用 55纳米的C55DDC工艺技术构建。这款超低功耗芯片采用了 icyflex-V RISC-V 内核,集成了 256KB RAM 和 4KB ROM。CSEM 科学家在 2019 年发表的一份技术报告中告诉了我们更多关于基于 RISC-V 架构超低功耗处理器的信息。其实,这种 4 级流水线架构实现了支持压缩指令和乘法的 RV32IMC ISA。

这款新开发的 RISC-V 芯片支持实时模式切换,有助于保持电源效率和性能。它能够共存各种版本的低功耗模式(用于慢速和保持模式)和高速(用于快速模式)模式。根据EENews Europe 提供的更多细节,我了解到,该款芯片在默认情况下处于 50 kHz 的慢速模式,并且可以在 8 MHz 时切换到快速模式。在慢速模式下功耗为 10 µA,在快速模式下功耗为250 µA。在不活动期间,该芯片在始终开启的 32KHz 时钟下功耗大约为 1µA。

如果你对这则新闻感兴趣,可以访问 CSEM的press room页面。

文章翻译者:Taylor Lee,瑞科慧联(RAK)高级嵌入式开发工程师,有丰富的物联网和开源软硬件经验,熟悉行业主流软硬件框架,对行业发展动向有着敏锐的感知力和捕捉能力。